# TOFPET: a High-Performance ASIC for Time-of-Flight Applications

Luis Ferramacho

DIRC 2015 13 November 2015

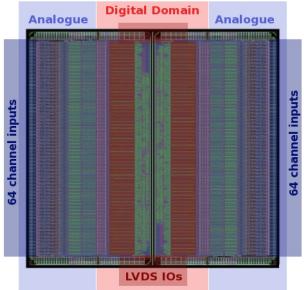

#### **TOFPET ASIC**

- 2 x 64 channels in 7 x 7 mm2

- CMOS 130nm

- Frontend + TDC + Digital readout

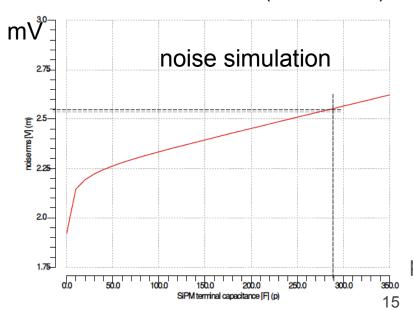

- Optimum SNR performance for SiPM with capacitance up to 350 pF

- Positive or negative signal polarity

- SNR (Qin = 200 fC): 25 dB

- Interpolation TDC

- Time binning: 50 ps (option 25 ps)

- Optimized for low power

- 8-11 mW channel

- Digital I/O LVDS

- Output data rate 640 Mb/s

- On-chip calibration circuitry

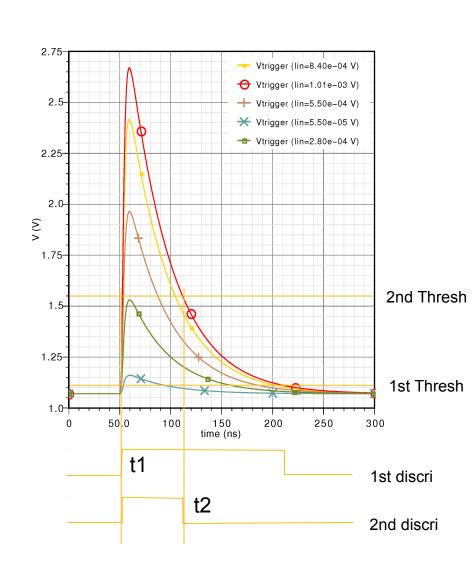

## Time and amplitude measurement

- Threshold for time measurement adjustable in the range 0.5-15 p.e.

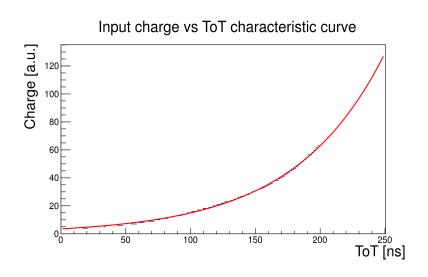

- Time-over-Threshold (ToT) with second discriminator

- Second discriminator used for trigger

- TDCs generate the time stamps t1 and t2

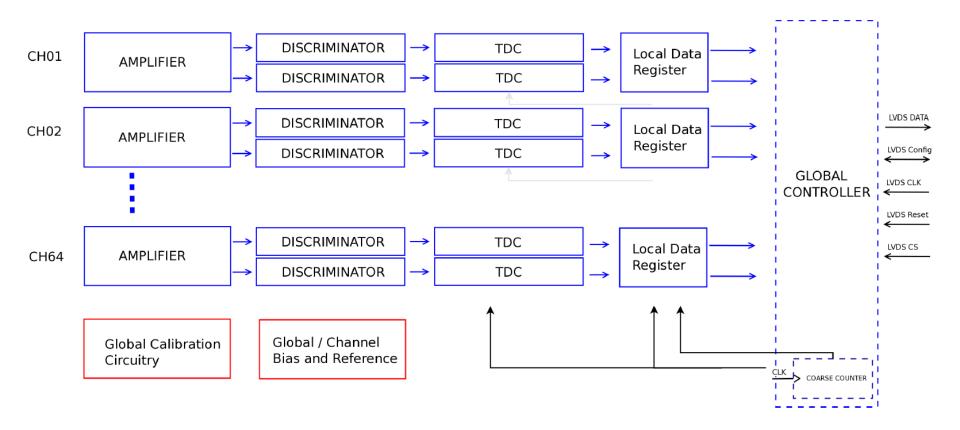

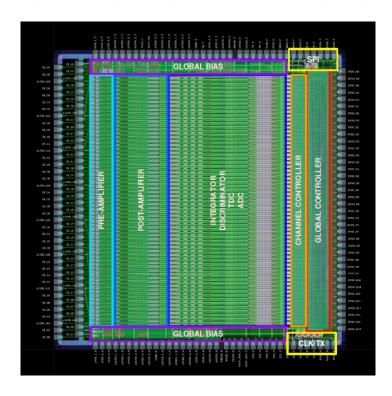

## **Overall chip architecture**

- The TOFPET ASIC consists of a 64-channel analogue block, calibration circuitry, golden-references and bias generators and a global controller.

- Two transimpedance amplifier stages per channel: for time and energy measurement (trigger, shaped signals)

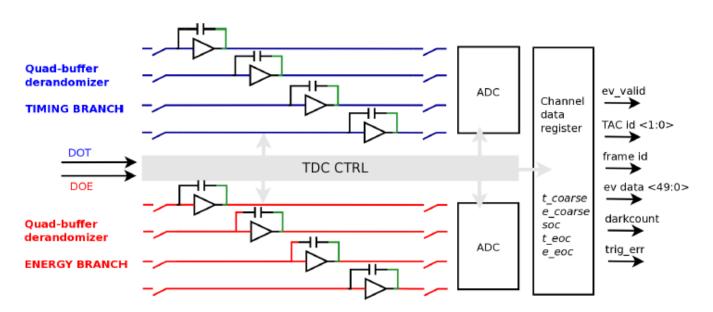

## Time-to-digital converters

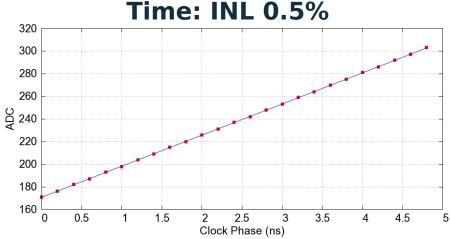

- TDC with 25ps/50ps time binning based on analogue interpolators

- TDC Control: switching, hit validation, buffer allocation, data reg.

- Four TACs and data FIFOs per channel allow rate per channel of 160 kHz with negligible deadtime

- Time stamp: 10-bit master clock count + 10-bit fine time counter

## **Output data**

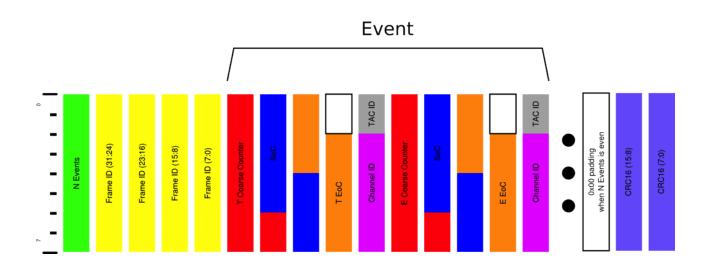

- The ASICs transmits data in frames, each frame consisting of the events captured in a 1024 clock period (6.4 µs frames).

- Up to 48 events per frame can be captured, each event including time counters and channel ID.

- Max output rate is 6 M events/s

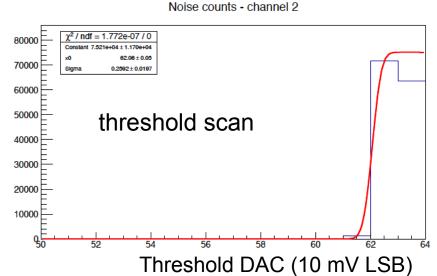

#### **Dark counts**

- Innovative scheme for dark count rejection without triggering the TDC

- For SiPM characterization, a dark count meter per channel is available.

- Each channel has an embedded counter, incremented each time a signal triggers the low threshold but not the high threshold.

## **Summary of ToFPET chip specs**

- Signal conditioning and discrimination circuitry and two high-performance TDCs for each of the 64 independent channels.

- TDC time binning: 50 ps (option 25 ps)

- Intrinsic time resolution 21 ps r.m.s.

- Charge measurement with time-over-threshold

- Dynamic range: 300 pC

- SNR (Qin = 200 fC): 25 dB

- Coarse Gain: G0, G0/ 2, G0/ 4

- SiPM family supported: positive or negative signal polarity

- On-chip Calibration Circuitry: internal pulse generator, programmable 6-bit amplitude

- Max Channel Hit rate: 160 kHz

- Max Output Data Rate: 320 Mb/s (640 Mb/s with double-data-rate)

- Fully digital output, 2 data LVDS links DDR compatible

- Operation frequency 80-160 MHz

- Power per Channel: 8-11 mW

- SiPM HV fine biasing: range 500 mV

## **TOFPET ELECTRONICS**

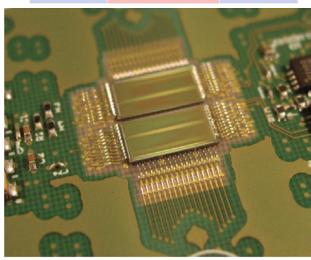

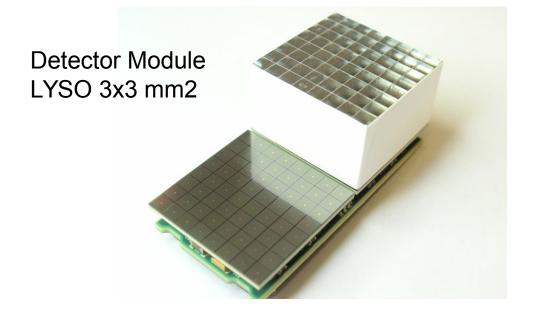

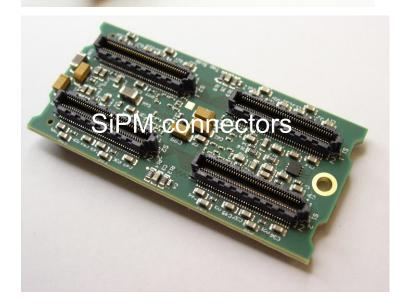

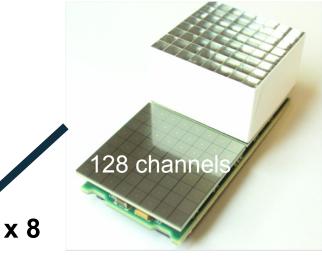

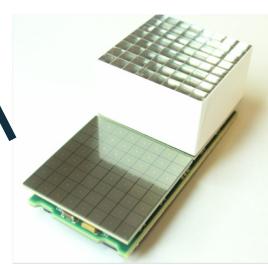

#### **TOFPET Frontend Board**

Our new, SiPM based, front end PET detector based on the TOFPET ASIC allows building the most compact PET detector ever.

Directly compatible with Hamamatsu 8x8 MPPC arrays

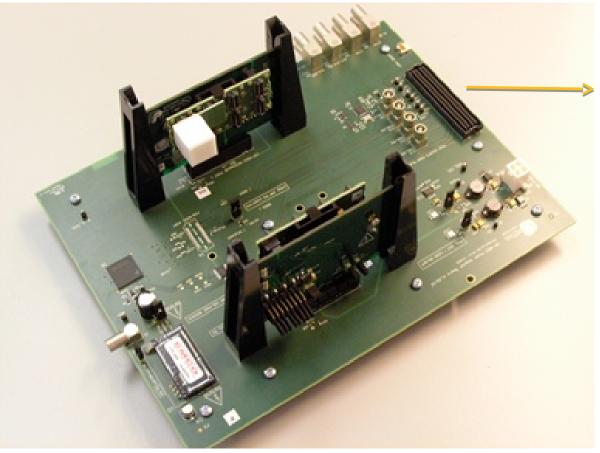

#### **TOFPET Evaluation Kit**

Two frontend boards and power adapter board Mezzanines with crystal matrices are placed face-to-face

Connector to Virtex development kit and DAQ

## **DAQ** system

#### FEB/D Board:

- Data concentration and filtering based on Kintex 7

- Motherboard serving 1024 independent channels

- Data readout and configuration of 8 frontend boards

- board-to-board or cable connection

- Output data serial links (1.6 Gbit/s) or high-speed optical links (2x8 Gbit/s)

- Daisy chaining of data and configuration links

- On board DC-DC converters (24 V external supply)

- On board SiPM bias voltage regulation (64 lines)

#### **DAQ Board:**

- 12 data links (electrical or optical) with total bandwidth 96 Gb/s

- Clock and synchronization signals

- Coincidence trigger in Kintex 7

# Allows building a PET scanner with many 10'000 channels

1024 channels

x 12

FEB/D daisy chaining allows to extend the total number of cannels

## TOFPET PERFORMANCE

## Single photon pulse and noise

#### Low-noise frontend

- Single photo-electron pulse amplitude is 40 mV

- Measured noise is 2.6 mV

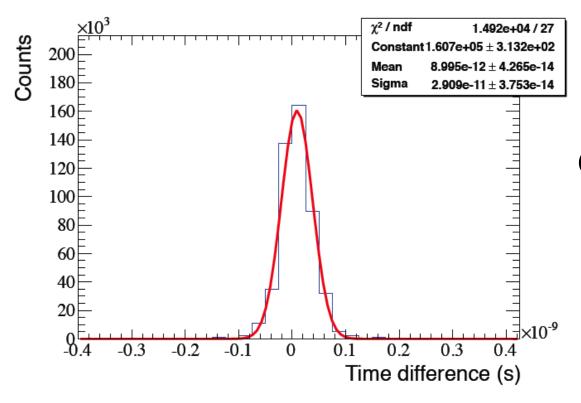

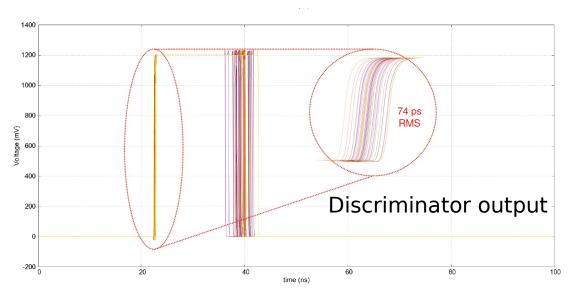

#### Intrinsic time resolution

Distribution of the time difference between two channels triggered simultaneously by test pulse

Channel resolution

σ= 21 ps r.m.s.

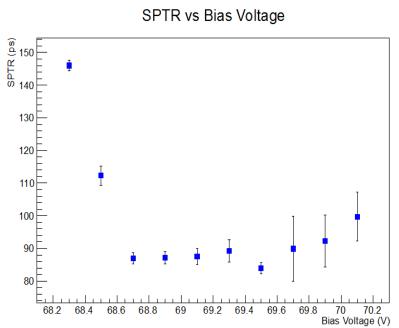

#### **SPTR** measurements

#### Single photon time resolution Measurements with PiLAS 420 nm laser light

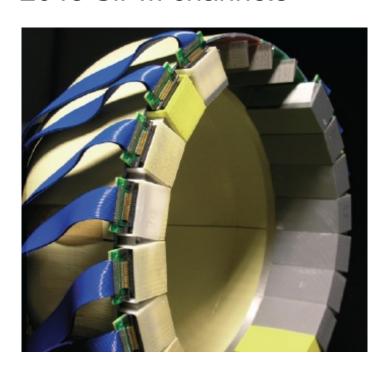

## **TOFPET demonstrator ring**

- PET Scanner demonstrator ring

- inner diameter of 230mm

- presently 2/3 equipped

- 16 Detector Modules

- 2048 SiPM channels

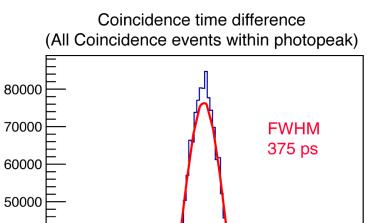

## **TOFPET** demonstrator: timing performance

Time difference [ns]

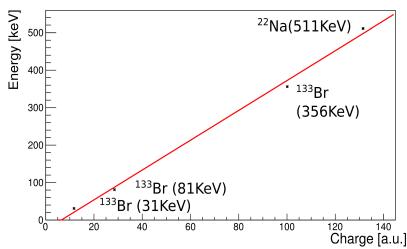

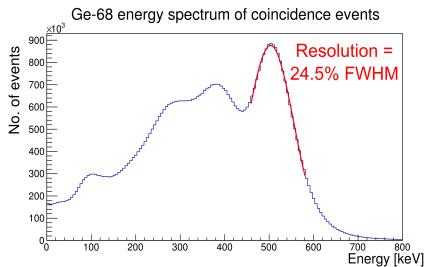

## **TOFPET** demonstrator: Energy resolution

#### Energy scale correction

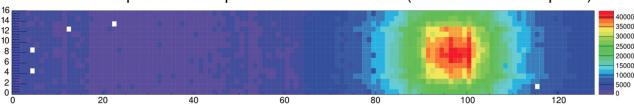

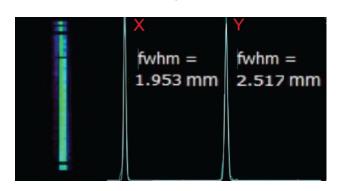

## **TOFPET demonstrator: Imaging**

#### **Reconstructed Spatial Resolutions**

#### Ge68 Line source (1.5 mm diameter)

#### Na22 Point source (1 mm radius)

## TOFPET2

### **TOFPET2**

- New version of TOFPET chip

- I/O remains the same (but twice output links)

- Improved timing measurement

- optimized for SiPM capacitance 320 pF

- Aiming at PET CTR of 200 ps

- Linear pre-amplifier in the range 0-1500 pC

- compatible with high gain SiPMs

- Linear charge integrator in the full dynamic range

- ToT remains an option

- Event rate up to 600 kHz per channel

- suitable for PET modules with light sharing

- Reduced power consumption

- 5-8 mW/channel

- Silicon options:

- low gain, low capacitance SiPMs

- high gain, high capacitance SiPMs

- Submitted for fabrication

## Newest version of the TOFPET ASIC

CMOS 110 nm Die size 5x5 mm2

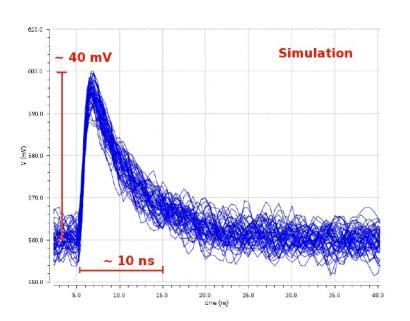

## **TOFPET2:** full chip simulation

## **Single-Photon Time Resolution:**

$\sigma$ =39 ps RMS (G: 3.5x10<sup>6</sup>)

$\sigma$ =74 ps RMS (G: 1.2x10<sup>6</sup>)

## **TOFPET2** design specs

- Signal amplification and discrimination for each of 64 independent channels.

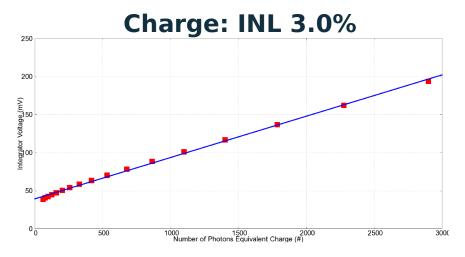

- Dual branch quad-buffered analogue interpolation TDCs for each channel. The first branch is used for timing measurement. The second branch can either be used for time-over-threshold (ToT) or charge measurement (ADC).

- Quad-buffered charge integration for each channel.

- Dynamic range: 1500 pC.

- SNR (Qin = 200 fC): 25 dB.

- TDC time binning: 50 ps (option 25 ps).

- Gain adjustment per channel: 1, 1/2, 1/4, 1/8.

- SiPM family supported: positive or negative signal polarity (terminal capacitance up to 320 pF guarantees SNR as above stated).

- On-chip calibration circuitry: internal pulse generator with programmable amplitude.

- Max channel hit rate: 600 kHz.

- Rejects dark counts without triggering, allowing to handle in excess of 1 MHz of dark counts.

- Configurable timing, trigger and ToT thresholds.

- Fully digital output, 4 LVDS data links DDR compatible.

- Low latency trigger data (channels above threshold)

- Max output data rate: 3.2 Gb/s.

- Operation frequency: 200 MHz.

- Power per channel: 5-8 mW.

For more information visit www.petsyselectronics.com or send email to info@petsyselectronics.com

Thank you for your attention